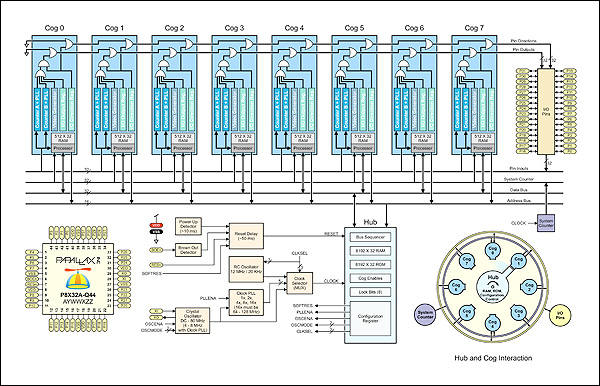

The Parallax Propeller is a powerful and flexible micro controller available in DIP, QFP, and QFN packages.

The "native" languages of the Propeller are SPIN and PASM. The Propeller JVM is implememnted using both languages. Spin like Java is a byte-code interpreted language. The Propeller ASM language is used to interpret Spin and Javelin Java byte-codes.

Spin is an object.method language which does not offer inheritance, shared object references, or polymorphism. Despite these minor shortcomings, Spin is a capable and flexible language that fits the Propeller nicely.

The Propeller can be programmed in Spin/PASM, Basic, C ANSI-C89, Javelin Java and other languages. An emulated GNU tools effort is underway.

Propeller P8x32a Features/Collateral:

The Parallax Propeller is a unique micro controller. It is unique because it is so different from other micro controllers. While some of the differences are seen as weak points with respect to adoption by many who come to expect certain things from micro controllers, the differences are strengths to those of us who enjoy or don't mind learning new things.